可控分频器&Modelsim仿真

简介

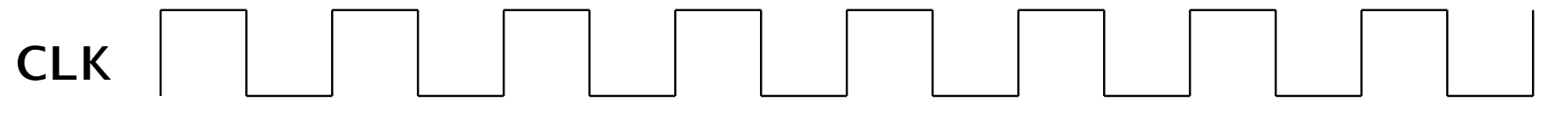

啥是分频器呢?首先我们知道如果有一个时钟信号$CLK$的波形如下:

那么我们定义一个$Q$,每当接收到时钟信号的上升沿,则变一次电平,那么就是这样:

这样我们就得到了$Q$的频率为$CLK$的一半。

而我们的试验箱中有一个频率为$50MHz$的时钟信号源,我们要做的就是通过分频,获得频率为学号后四位以及后五位的信号,对我来说就是$3035Hz$以及$13035Hz$。

此次实验需要使用$Modelsim$进行仿真。

过程

$50MHz=50\\times10^6Hz\\ 50\\times10^6\\div 3035 =16474\\16474\\div2=8237 $

那么我们用$Q$当作计数器,每接受$8237$次来自$CLK$的上升沿信号,$c0$就反转一次,测$c0$就约是$3035Hz$的频率了。

同时这次实验需要学会如何为$Modelsim$写仿真测试文件:

1 |

|

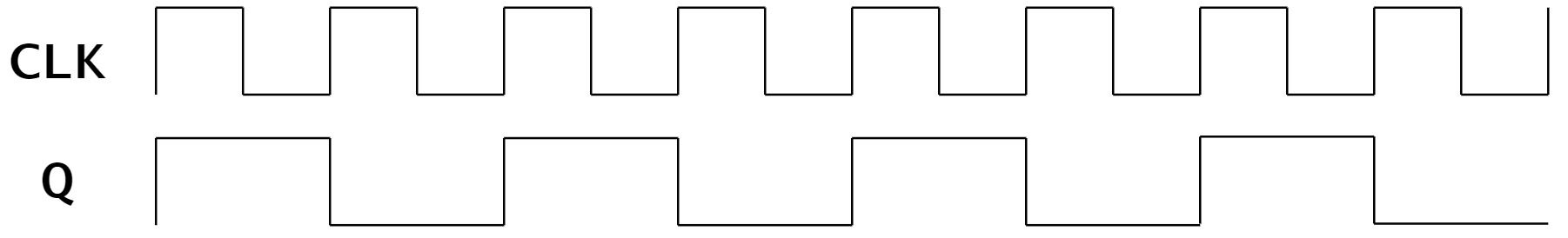

通过这张图我们可以看到,$clk$确实每$10ns$翻转一次,且 $50ns$时$en$从$0$跳变至$1$。

代码

测试文件 $test\underline{}gal\underline{}3035\underline{}4.v$

1 |

|

分频器代码 $gal\underline{}3035\underline{}4.v$

1 | module gal_3035_4(clk,c0,Q,en,x); |

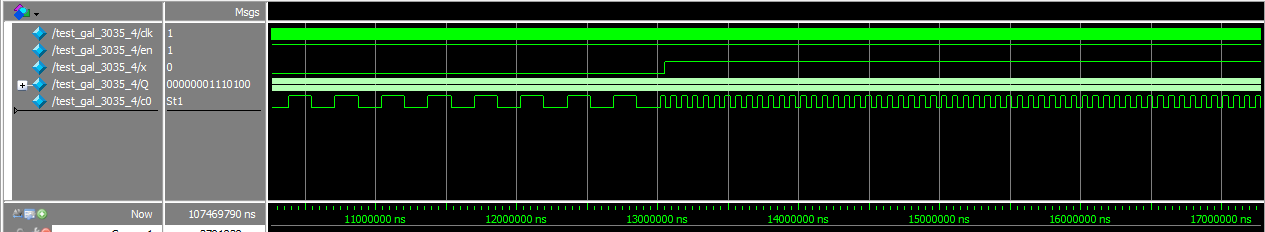

仿真波形

从上图可以看到在$13049230ns$之后$c0$的频率明显加快了,这里对应了测试文件第$17$行的x = 1。

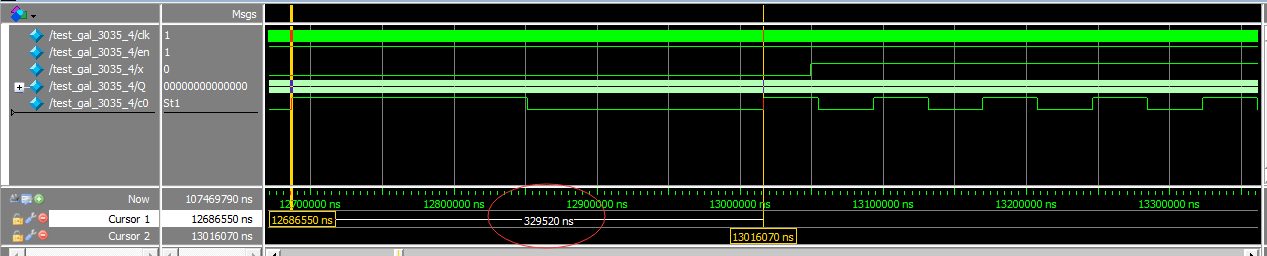

放大一点去观察的话,插入两个$Cursor$,下图红圈圈出的数为两个$Cursor$之间的时间,即周期。

$T=329520ns\\f=\frac{1}{T}=3035Hz$

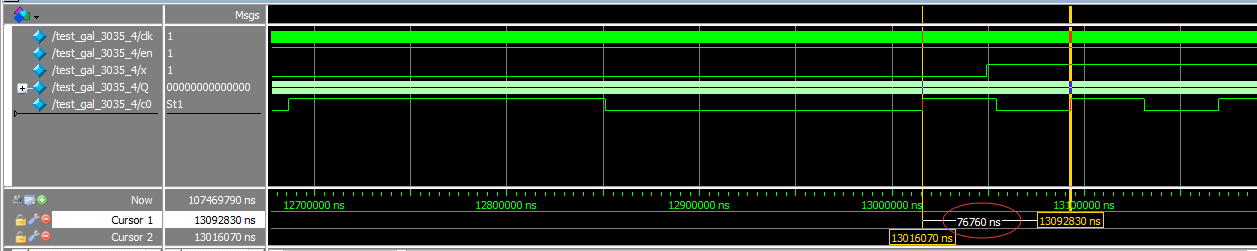

再看另一部分:

$T=76760ns\\f=\frac{1}{T}=13028Hz$

这里存在$10Hz$以内的误差。

引脚分配

$Family:Cyclone\ IV\ E\ \ \ \ \ \ \ \ Device:EP4CE22E22C8$

| 信号名 | 主板器件 | PIN |

|---|---|---|

| co | LED0 | 46 |

| clk | 50MHz | 90 |

| en | KEY2 | 30 |

| x | KEY1 | 31 |